TECHNICAL UNIVERSITY OF CLUJ-NAPOCA

**DIPLOM THESIS PROJECT**

# CoreSim: A Simulator for Evaluating LISP Mapping Systems

Author: Florin-Tudorel CORAŞ Supervisors: Phd. Virgil DOBROTĂ Phd. Albert CABELLOS Loránd JAKAB

# Contents

| Contents<br>List of Figures |      |                                                   |                          |  |  |  |  |  |  |

|-----------------------------|------|---------------------------------------------------|--------------------------|--|--|--|--|--|--|

|                             |      |                                                   |                          |  |  |  |  |  |  |

|                             | 1.1  | Problem Statement                                 | 4                        |  |  |  |  |  |  |

|                             |      | 1.1.1 The scalability of the Routing System       | 4                        |  |  |  |  |  |  |

|                             |      | 1.1.2 The Overloading of the IP Address Semantics | 5                        |  |  |  |  |  |  |

|                             | 1.2  | Current State and Solution Space                  | 5                        |  |  |  |  |  |  |

|                             |      | 1.2.1 Initial Research                            | 5                        |  |  |  |  |  |  |

|                             |      | 1.2.2 New Proposals                               | 7                        |  |  |  |  |  |  |

|                             | 1.3  | Current Implementations                           | 9                        |  |  |  |  |  |  |

| 2                           | The  | pretical Fundamentals                             | 10                       |  |  |  |  |  |  |

| -                           | 2.1  |                                                   | 10                       |  |  |  |  |  |  |

|                             | 2.1  | 1 1 1                                             | 10                       |  |  |  |  |  |  |

|                             |      |                                                   | 11                       |  |  |  |  |  |  |

|                             | 2.2  | Locator/Identifier Separation Protocol (LISP)     | 13                       |  |  |  |  |  |  |

|                             | 2.2  |                                                   | 16                       |  |  |  |  |  |  |

|                             | 2.3  | 1                                                 | 18                       |  |  |  |  |  |  |

|                             | 2.0  |                                                   | 18                       |  |  |  |  |  |  |

|                             |      |                                                   | 21                       |  |  |  |  |  |  |

| 3                           | Desi | an                                                | 23                       |  |  |  |  |  |  |

| 5                           | 3.1  | 8                                                 | 23<br>23                 |  |  |  |  |  |  |

|                             | 5.1  |                                                   | $\frac{23}{23}$          |  |  |  |  |  |  |

|                             |      | 1                                                 | 25<br>25                 |  |  |  |  |  |  |

|                             | 3.2  |                                                   | 25<br>25                 |  |  |  |  |  |  |

|                             | 5.2  | •                                                 | 25<br>25                 |  |  |  |  |  |  |

|                             |      |                                                   | $\frac{25}{26}$          |  |  |  |  |  |  |

|                             |      |                                                   | 20<br>26                 |  |  |  |  |  |  |

|                             |      | 3.2.4 Deciding upon a programming language        |                          |  |  |  |  |  |  |

|                             |      |                                                   | 20<br>27                 |  |  |  |  |  |  |

|                             | 3.3  | •                                                 | $\frac{27}{27}$          |  |  |  |  |  |  |

|                             | 5.5  | 1 85                                              | $\frac{27}{28}$          |  |  |  |  |  |  |

|                             |      |                                                   | 20<br>30                 |  |  |  |  |  |  |

|                             |      | 3.3.3       Design constraints                    | 31                       |  |  |  |  |  |  |

|                             |      | 3.3.4 Internal components                         | 32                       |  |  |  |  |  |  |

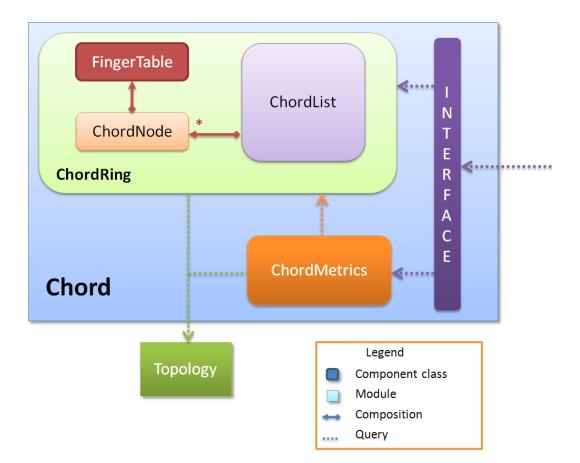

|                             | 3.4  | Chord Module                                      | 32<br>34                 |  |  |  |  |  |  |

|                             | 5.1  |                                                   | 34                       |  |  |  |  |  |  |

|                             |      | 3.4.2     Internal Components                     |                          |  |  |  |  |  |  |

|                             |      |                                                   | $\mathcal{I}\mathcal{I}$ |  |  |  |  |  |  |

|               |      | 3.4.3    | Routing and Metrics    |       |       | •   | •   |     |     | • |       |     |     | • | • | <br>• | • |   |     |    |

|---------------|------|----------|------------------------|-------|-------|-----|-----|-----|-----|---|-------|-----|-----|---|---|-------|---|---|-----|----|

|               | 3.5  | ALT M    |                        |       |       |     |     |     |     |   |       |     |     |   |   |       |   |   |     |    |

|               |      | 3.5.1    | Topology Design and    | Issue | es.   | •   | • • |     | • • | • | <br>• | ••• | • • | • | • | <br>• | • | • | ••• |    |

|               |      | 3.5.2    | Internal Components    |       | •••   | •   | •   |     | • • | • |       |     |     | • | • | <br>• | • |   |     |    |

|               |      | 3.5.3    | Routing and Metrics    |       | •••   | •   | •   |     | • • | • |       |     |     | • | • | <br>• | • |   |     | 39 |

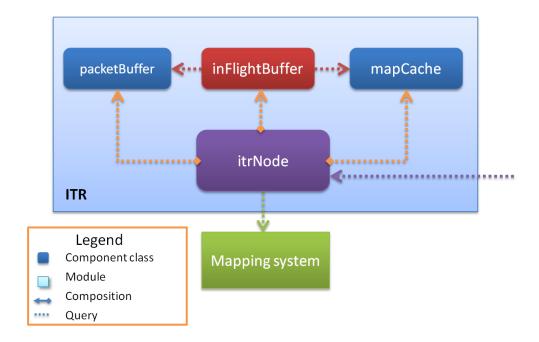

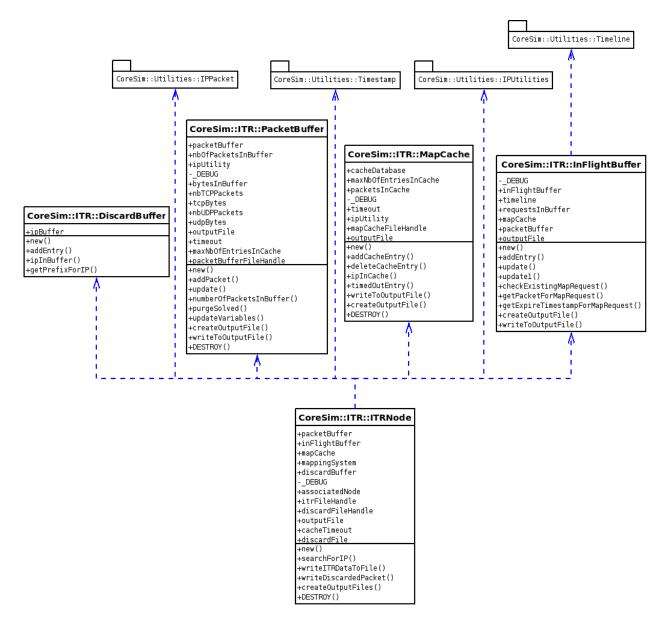

|               | 3.6  | ITR .    |                        |       |       | •   | •   |     |     | • |       |     |     | • | • | <br>• | • |   |     | 41 |

|               |      | 3.6.1    | Internal Components    |       |       | •   | •   |     |     | • |       |     |     | • | • | <br>• | • |   |     | 41 |

|               |      | 3.6.2    | Time constraints       |       |       | •   | •   |     |     | • |       |     |     | • | • |       |   |   |     | 42 |

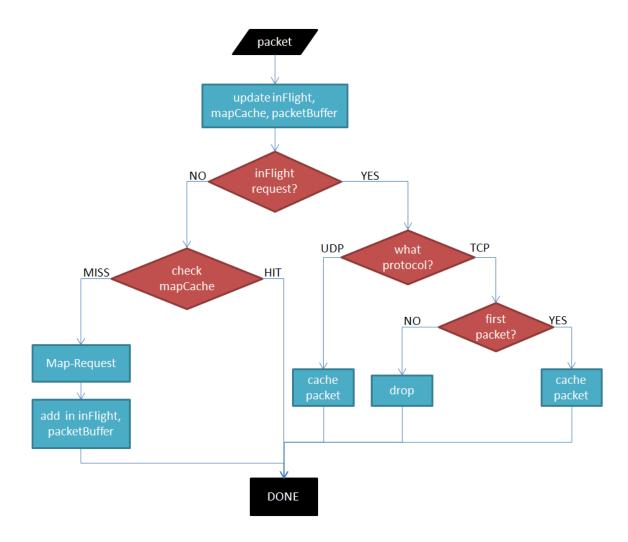

|               |      | 3.6.3    | ITR Cache policy and   | pack  | ket f | low | •   |     |     | • |       |     |     | • | • |       |   |   |     | 43 |

|               | 3.7  | DBI .    |                        |       |       | •   | •   |     |     | • |       |     |     | • | • |       | • |   |     | 44 |

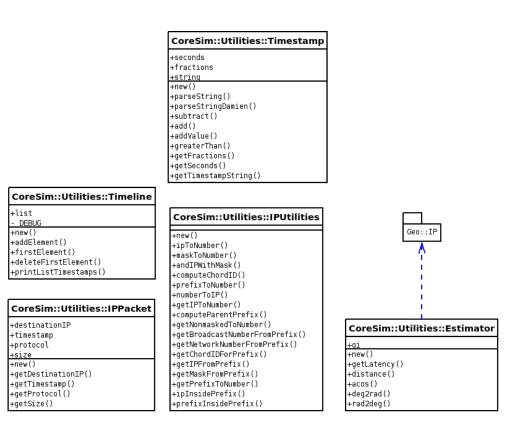

|               | 3.8  | Utilitie | s                      |       |       | •   | •   |     |     | • |       |     |     | • | • |       | • |   |     | 44 |

|               |      | 3.8.1    | Timeline               |       |       | •   |     |     |     | • |       |     |     | • |   |       | • |   |     | 44 |

|               | 3.9  | Scenar   | 0                      |       |       |     | •   |     |     | • |       |     |     | • |   |       |   |   |     | 45 |

|               |      | 3.9.1    | UCLouvain trace file   |       |       |     | •   |     |     | • |       |     |     | • |   |       |   |   |     | 45 |

|               |      | 3.9.2    | UPC trace files        |       |       | •   | •   |     |     | • |       |     |     | • |   |       |   |   |     | 45 |

|               | _    |          |                        |       |       |     |     |     |     |   |       |     |     |   |   |       |   |   |     |    |

| 4             | -    |          | al Results             |       |       |     |     |     |     |   |       |     |     |   |   |       |   |   |     | 46 |

|               | 4.1  | -        | Files Examples         |       |       |     |     |     |     |   |       |     |     |   |   |       |   |   |     |    |

|               |      | 4.1.1    | itrOutput File         |       |       |     |     |     |     |   |       |     |     |   |   |       |   |   |     |    |

|               |      | 4.1.2    | mapCache File          |       |       |     |     |     |     |   |       |     |     |   |   |       |   |   |     |    |

|               |      | 4.1.3    | inFlightBuffer File .  |       |       |     |     |     |     |   |       |     |     |   |   |       |   |   |     |    |

|               |      | 4.1.4    | packetBuffer File      |       |       |     |     |     |     |   |       |     |     |   |   |       |   |   |     |    |

|               | 4.2  |          | Implemenation Validati |       |       |     |     |     |     |   |       |     |     |   |   |       |   |   |     |    |

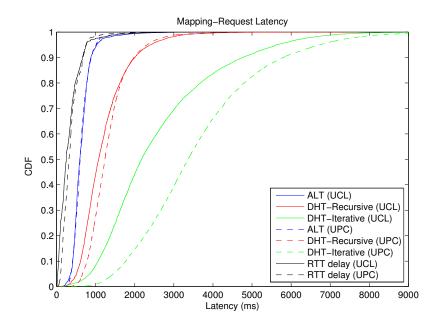

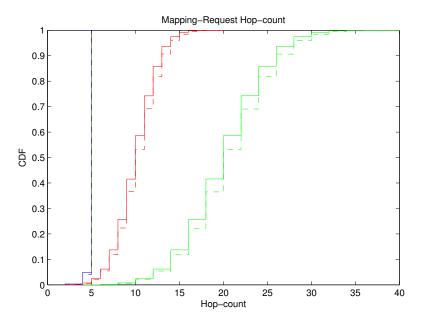

|               | 4.3  | Mappir   | ng Latency             |       | •••   | •   | •   |     | • • | • |       |     |     | • | • | <br>• | • |   |     | 48 |

|               | 4.4  | Cache    | Miss                   |       |       | •   | •   |     |     | • |       |     |     | • | • | <br>• | • |   |     | 50 |

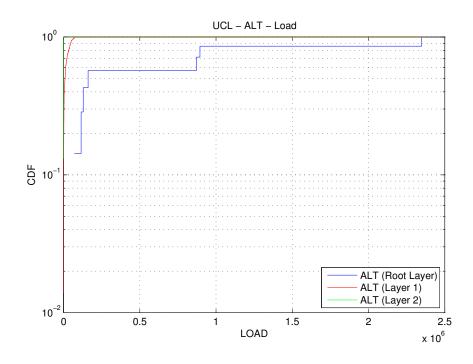

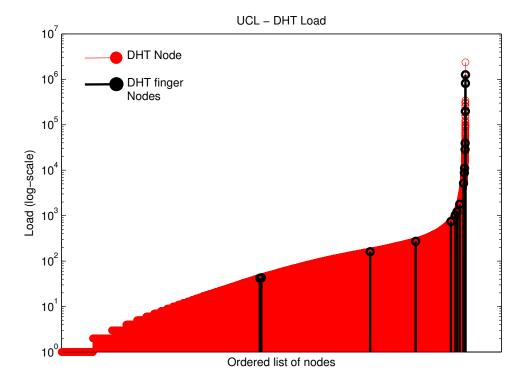

|               | 4.5  | Node L   | load                   |       |       | •   | •   |     |     | • |       |     |     | • | • | <br>• | • |   |     | 50 |

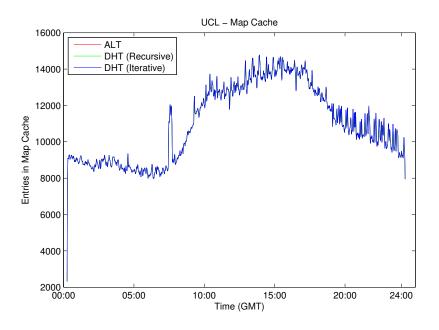

|               | 4.6  | EID-to   | -RLOC Cache Size .     |       |       | •   | •   | ••• | • • | • | <br>• | ••• | • • | • | • | <br>• | • | • | ••• | 53 |

| 5             | Con  | clusions |                        |       |       |     |     |     |     |   |       |     |     |   |   |       |   |   |     | 55 |

|               |      |          |                        |       |       |     |     |     |     |   |       |     |     |   |   |       |   |   |     |    |

| References    |      |          |                        |       |       |     |     |     |     |   | 57    |     |     |   |   |       |   |   |     |    |

| Abbreviations |      |          |                        |       |       |     |     |     | 61  |   |       |     |     |   |   |       |   |   |     |    |

| A             | Rest | ılts     |                        |       |       |     |     |     |     |   |       |     |     |   |   |       |   |   |     | 62 |

| В             | UM   | L Diagra | ams                    |       |       |     |     |     |     |   |       |     |     |   |   |       |   |   |     | 67 |

|               |      |          |                        |       |       |     |     |     |     |   |       |     |     |   |   |       |   |   |     |    |

# **List of Figures**

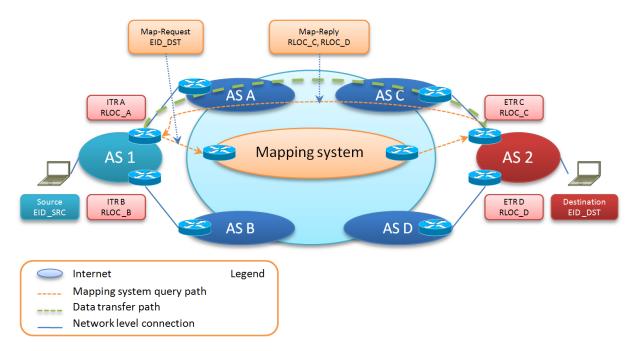

| LISP Topology Example                                     | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

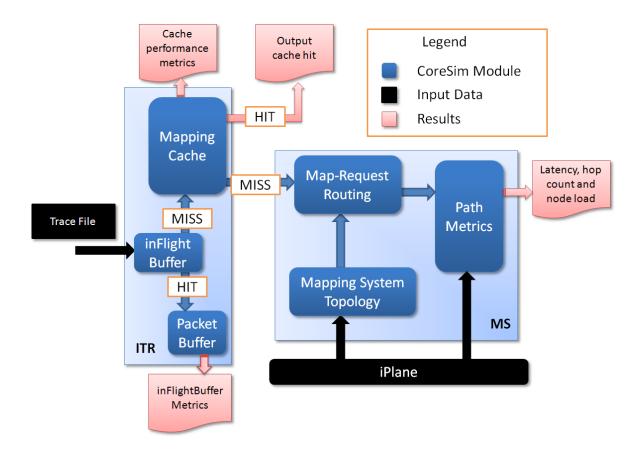

| CoreSim Architecture                                      | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

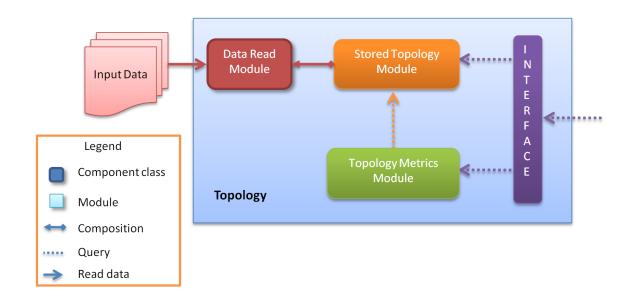

| Topology Module Block Diagram                             | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

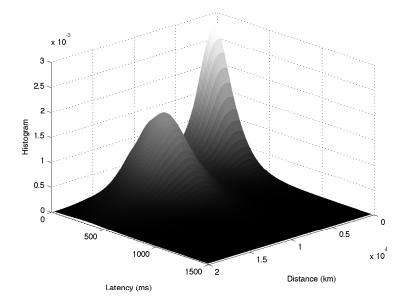

| 3D histogram (latency vs. distance)                       | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

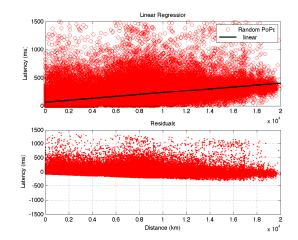

| Scatter Plot and Linear Regression (latency vs. distance) | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

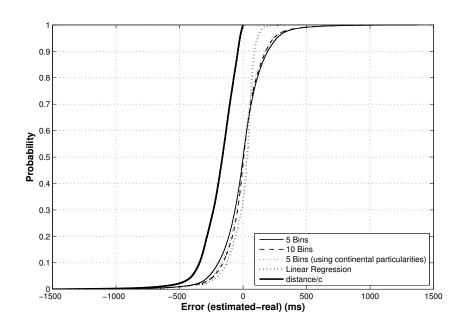

| Error of the Estimators                                   | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

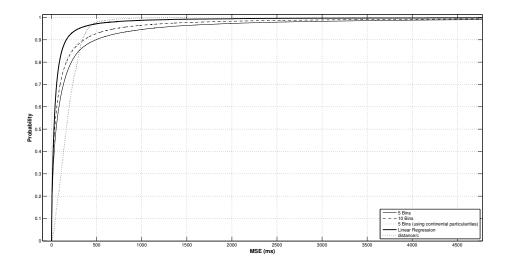

| Mean Square Error of the Estimators                       | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Chord Block Diagram                                       | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1 11 0                                                    | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                           | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ALT Module Block Diagram                                  | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                           | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                           | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ITR Flowchart                                             | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Mapping Latency distribution                              | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Hop count distribution                                    | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

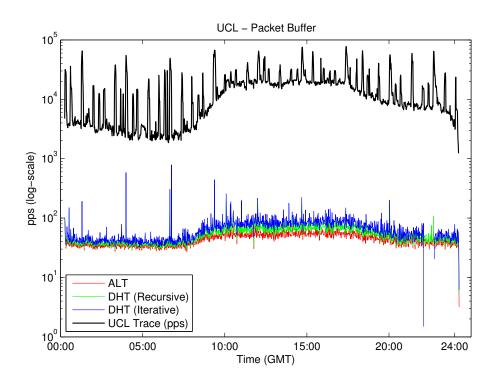

| Evolution of the miss rate over time                      | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                           | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

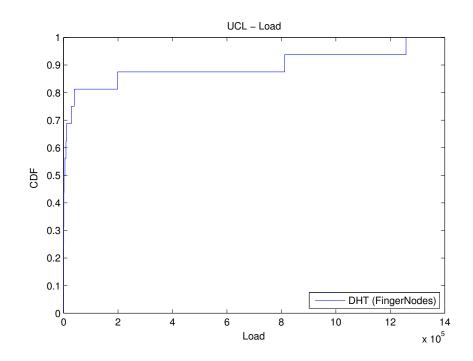

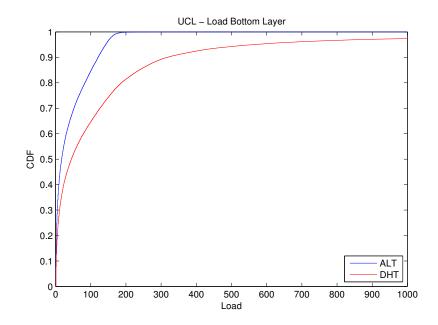

| UCL LISP-DHT Ordered Load                                 | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Evolution of the map cache with the day                   | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

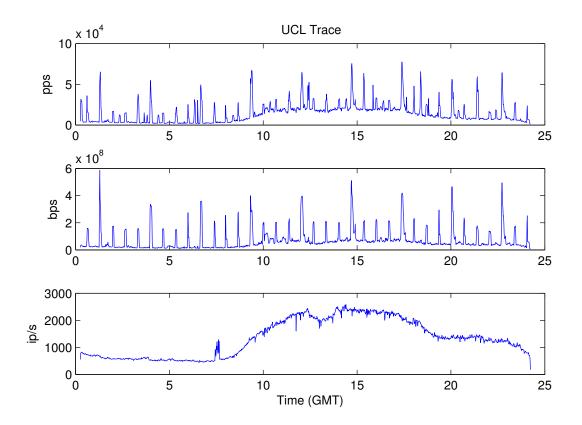

| UCL Trace File                                            | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

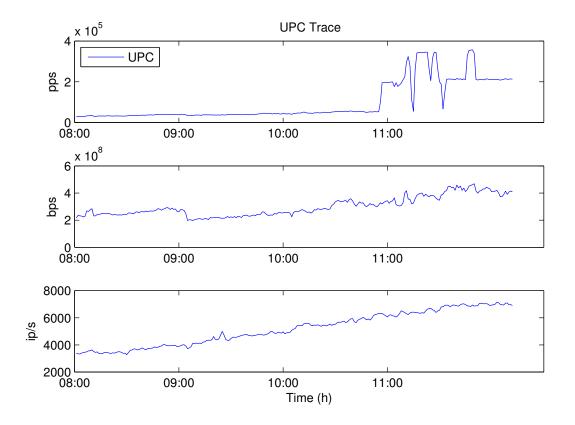

| UPC Trace File                                            | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                           | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                           | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

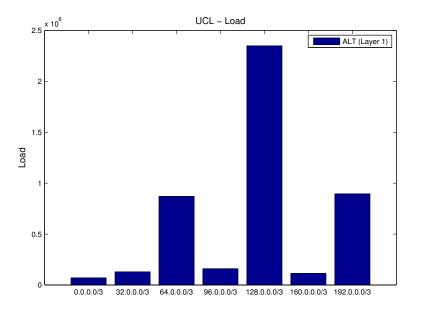

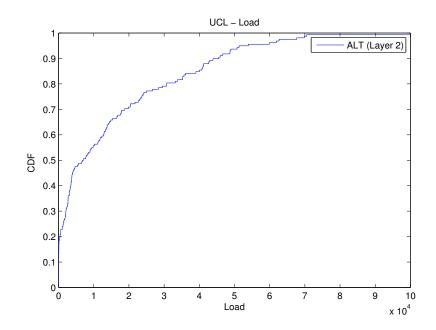

| UCL Distribution of the load on layer 2 in LISP+ALT       | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                           | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

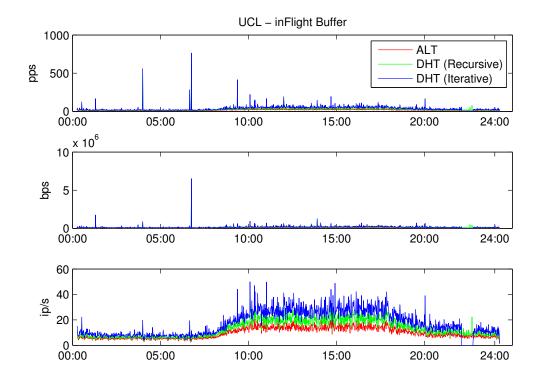

| UCL inFlightBuffer                                        | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

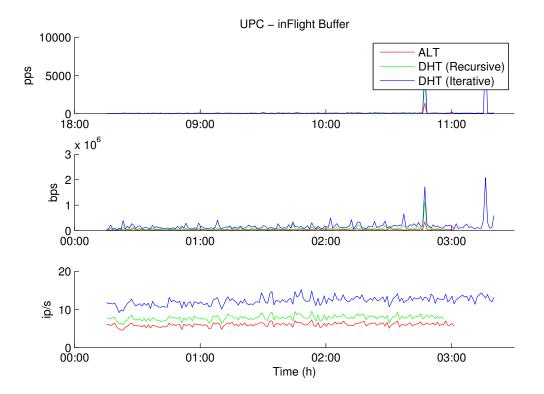

| UPC inFlightBuffer                                        | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

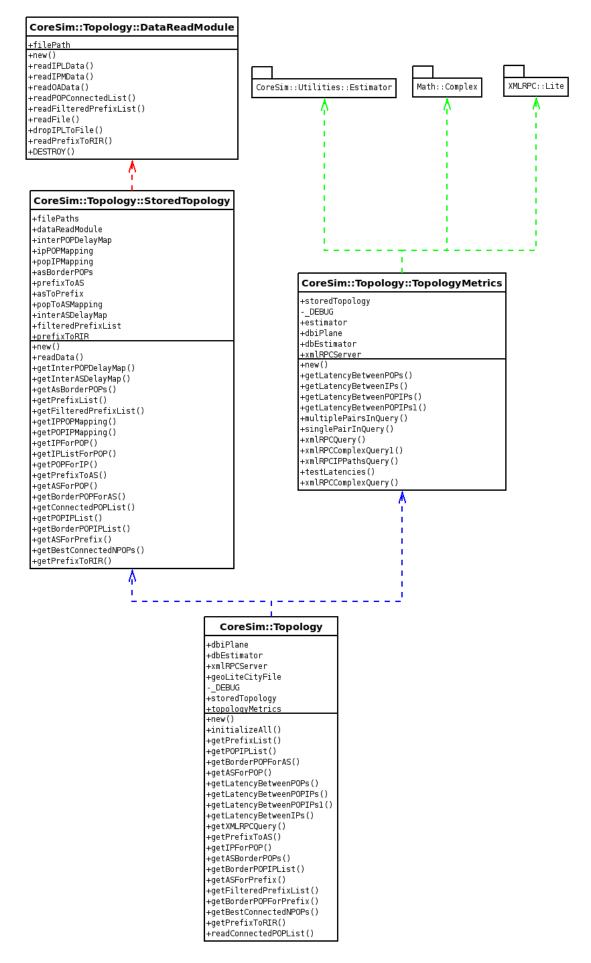

| Topology Module UML Diagram                               | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

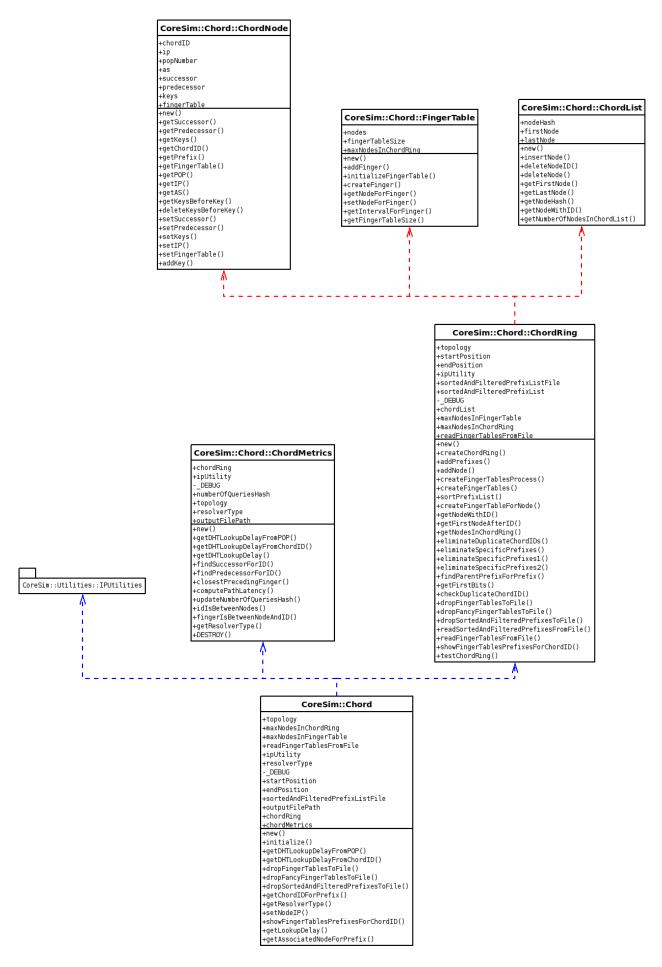

| Chord Module UML Diagram                                  | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

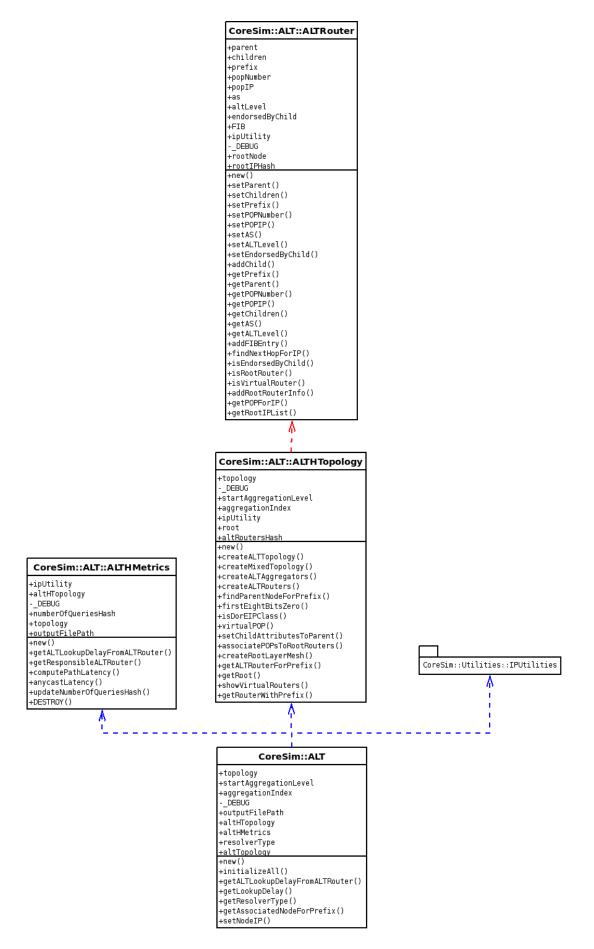

|                                                           | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                           | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                           | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                           | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

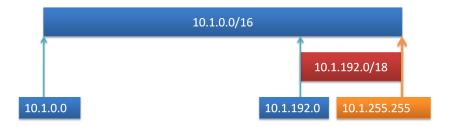

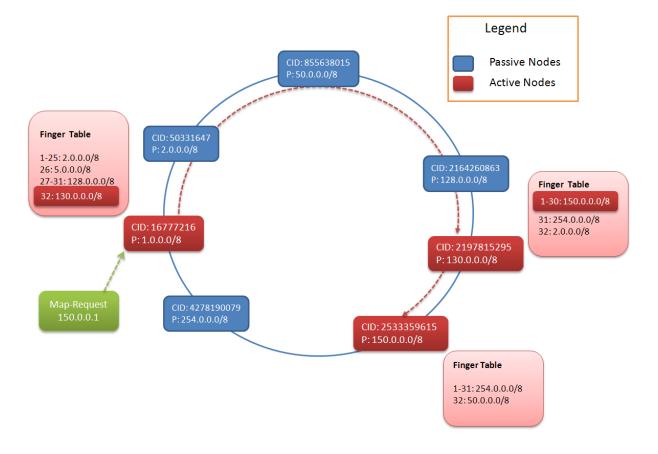

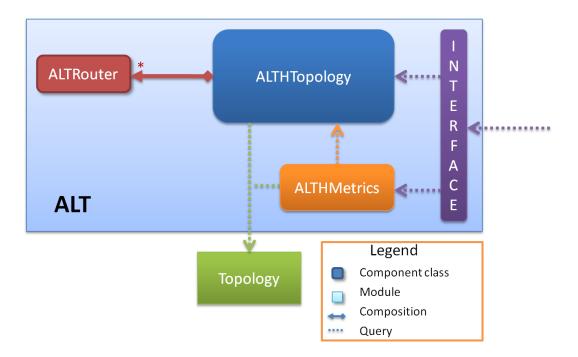

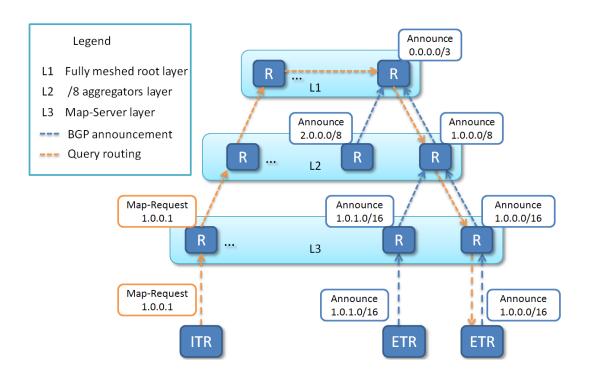

|                                                           | CoreSim Architecture       7         Topology Module Block Diagram       30         Bistogram (latency vs. distance)       5         Scatter Plot and Linear Regression (latency vs. distance)       5         Error of the Estimators       6         Mean Square Error of the Estimators       7         Chord Block Diagram       7         Example of Prefixes Overlapping       1         LISP-DHT Topology Example       7         ALT Module Block Diagram       7         LISP-ALT Topology Example       7         ALT Module Block Diagram       7         ITR Module Block Diagram       7         ITR Module Block Diagram       7         ITR Flowchart       7         Mapping Latency distribution       7         Hop count distribution       7         Hop count distribution       7         Evolution of the map cache with the day.       7         UCL LISP-DHT Ordered Load       7         UVCL Trace File       7         UVCL LISP-DHT Fingers Load       7         UVCL Distribution of the load on layer 1 in LISP+ALT       7         UVCL Distribution of the load on layer 2 in LISP+ALT       7         UVCL Distribution of the load on layer 3 in LISP+ALT       7 |

# **Chapter 1**

# State-of-the-art

# 1.1 Problem Statement

In October 2006 the Internet Advisory Board (IAB) held a Routing and Addressing Workshop in Amsterdam, Netherlands with the goal of developing a shared understanding of the problems that the large backbone operators are facing regarding the scalability of the Internet routing system. The outcome of the meeting, their findings and suggestions, have been summed up in a Request For Comments (RFC 4984)[MZF07] and forms the input to the Internet Engineering Task Force (IETF) community which aims to identify the next steps towards effective solutions.

While many aspects of a routing and addressing system were discussed, the participants deemed two as most important and subsequently formulated two problem statements:

- Problem 1: The scalability of the Routing System

- Problem 2: The Overloading of the IP Address Semantics

An in depth analysis of the problems (including the two above) affecting the routing system was also provided.

### 1.1.1 The scalability of the Routing System

The main parameter when discussing about the scalability of a routing system is the size of the Routing Information Base (RIB), because it limits the number of destinations in the system, a router knows about. It only follows that a routing system will, at a given moment in time, be hindered in its growth by the RIB size and this impairment will be surpassed only by economical means, that is upgrading the system. This is known as product life cycle and plans to replace old devices might follow some fixed time patterns but an increase in the speed of RIB fill up would lead to obsolete products before their time.

The Default Free Zone (DFZ) is no different and the above statements hold. Throughout the years, since the Internet's birth, the DFZ RIB shape[bgp09] of the growth curve has been the topic of much research and debate. There have been various hypothesis regarding the sources of the growth but the workshop participants settled on what they viewed the main driving forces behind the rapid growth of the DFZ RIB:

- Multihoming

- Traffic engineering

- Suboptimal RIR address allocations

- Business events such as mergers and acquisitions

All the above factors lead to prefix de-aggregation and subsequently to the rapid growth of the DFZ RIB through the injection of unaggregatable prefixes. This also exposes the core of the network to the dynamic nature of the edges and thus to an increased number of BGP UPDATE messages injected into the DFZ ("UPDATE Churn"). To make matters worse, it is predicted that the update churn situation will be exacerbated by the Regional Internet Registries(RIR) policies through which end sites are allocated Provider Independent (PI) addresses. These addresses are not topologically aggregatable. This situation is explained by the need of multihoming without the "provider lock" that Provider Aggregatable (PA) space creates and also due to renumbering costs which some enterprises find unacceptable in the case when PA addresses are provide.

It is worth mentioning that the deployment of IPv6 is regarded to lead to the RIB and Forward Information Base (FIB) size increase by a factor of four, in other words the situation will be everything but improved.

# 1.1.2 The Overloading of the IP Address Semantics

One of the assumptions providing support for routing scalability was stated by Yakov Rekhter:

#### "Addressing can follow topology or topology can follow addressing. Choose one"

Following this idea some authors [O'D97, Chi99] have tried to provide the architecture for a scalable routing system by making use of aggressive topological aggregation. Unfortunately there is some difficulty in creating and maintaining the envisioned congruence. This difficulty arises from the overloading of addressing with semantics of both end users identifiers and router locators: there is the need to identify both clients and routers and only one number space is available. Either way, the overloading has been felt and moreover deemed to have had profound implications for the scalability of the global routing system. A solution for this problem would be to assign the locator part of the IP address in such a way that it will be congruent with the Internet topology. However, these assignments are based on organizational criteria and gave birth and now feed the continual growth of an incongruence between the topology and addressing. It was the workshop participants conclusion that such a desideratum is not fulfillable by means of only one number space in the context of topological routing systems and a split of the "locator/identifier overload" of the IP address semantics would be necessary to scale the routing system. However, details about the architecture of such a system were not explored.

# 1.2 Current State and Solution Space

Since the days of the IAB workshop nothing has changed for the better in the DFZ, though is has changed for the worse proving right some of their predictions. In that sense the BGP routing table has grown from 200000 entries in 2006 to 300000 entries in 2009 [bgp09].

### 1.2.1 Initial Research

Over the years considerable effort was put into finding or investigating solutions for the scalable inter-domain routing, some proved to be dead ends and other sparked new ideas, out of them the author wants to acknowledge the following:

#### **MULTI6**

This IEFT Working Group (WG) was formed to explore the solution space of IPv6 multihoming and present proposals compliant to what was then the definition of the IPv6 with the goal of avoid-

ing route injection to the DFZ [ABG03]. Their solutions revolved around two ideas: the allocation of PI address space for customers, this is effectively the current implementation, and the second assigning multiple address prefixes to multihomed sites. The second solution implies the use of both ISP address spaces and when one fails the communication is moved to the other address. This was also the largest class of proposed solutions [van]. From a technical point of view both solutions were flawed because the first category does not scale and the second introduces fundamental changes to the Internet routing system. It was the opinion of the workshop participants that the solutions solved problems by introducing new ones for which solutions were not proposed, thus they are incomplete [MZF07].

#### SHIM6

When MULTI6 was not chartered for solutions a new WG, SHIM6, was formed. They picked up the second idea from the MULTI6 and decided upon a host based solution. The host IP stack includes a "shim" that presents a stable "Upper Layer Identifier" (ULID) to the upper layer protocols but may rewrite the IP packets in accordance with the currently working IP address for transmitted packets. It provides locator agility below the transport protocols, so that multihoming can be provided for IPv6 with failover and load spreading properties, without assuming that a multihomed site will have a PI address prefix which is announced in the global IPv6 routing table[shi]. Both the locator and the identifier were 128-bit IPv6 addresses the former belonging to the packets and the latter to the transport layer.

The problems with this solution were not few and the first, obvious, one is that it required the change of all the host stacks. Moreover there was no clear specification onto how end-to-end communications would take place in the context of multiple locators associated to a multihomed host [MZF07].

Important drawbacks were the lack of suport for Traffic Engineering (TE) at the service provider level and the need of performing renumbering when changing providers. It also implies additional state information on the host when considering that the remote communication end can be identified by multiple locators. This poses no problem for individual user hosts but it is a problem for servers which might have lots of ongoing connections[van].

Other open issues are related to ingres filtering done by ISPs through Access Lists(ACLs) and the question of acceptance of another header in the data packets.

#### GSE

It presented itself as an alternative addressing architecture for IPv6 which would control global routing growth by very aggressive topological aggregation and it did this by introducing another level of indirection. The proposal was to change the IPv6 address structure to bare the semantics of both an identifier and a locator. In this sense the first n bytes of the 16-byte IPv6 address are called the Routing Goop (RG), and are used by the routing system as locators. The last 8 bytes are the End System Designator (ESD), which specify an interface on the end-system. The rest of the bytes (16-n-8), which was belived to be around 2, form the Site Topology Partition (STP) which was described as Site-private "Lan Segment" information[O'D97]. The Site Border Routers need to rewrite the source RG of the site egress traffic to hide the internal site structure from the rest of the internet and also the destination RG of all the site ingress traffic, to hide the site's RG from all the internal routers.

The identifier/locator split requires that a mapping system is used to bind a set of locators to an identifier. For this purpose GSE proposed to use DNS, as a mapping service, but came short to providing solutions for locator failure recovery. Also, host stack modifications were required as the applications were allowed to use just the 8 bytes coresponding to the ESD[MZF07].

#### ENCAPS

This is a conceptual proposal and it is also built with the identifier/locator scheme in mind. The solution is different from the GSE one in the sense that it uses tunnels between the border routers instead of locator rewriting. In the envisioned system, the border router would read the destination and source addresses of a local site originated packet, do a mapping for these addresses (identifiers in fact) to locators by means of DNS and finally encapsulate the initial IP datagram with a new IP header containing the discovered locators and sends it to its proper destination. The border routers would compute routes between themselves by using existing routing protocols, may they be exterior gateway protocols like BGP or interior gateway protocols like OSPF or IS-IS[Hin96].

This solution avoids the conflicting needs of the ISPs and the customers for PA and PI prefixes by putting them in two different name spaces. Morover, this architecture provides a scalable multihoming solution with the advantage of no changes to the host stacks as the encapsulation is done by the border router. Also, it implies no changes to the practices of both applications and backbone operators[MZF07].

The proposal was by no means complete but, as it will be seen in the next section, it sparked ideeas for a new set of solutions in our time.

#### 1.2.2 New Proposals

#### LISP

The Locator/Identifier Separation Protocol [FFML09b] came as a response of the Amsterdam IAB Routing and Addressing Workshop problem statement and aims, as previously mentioned solutions, to solve the scalability of the routing system. One of the conclusions of the workshop was that any solution to the routing scalability is necessarily a cost/benefit tradeoff thus, given the high potential for gains of the indirection approach (a locator/identifier split), the map-and-encap ideea was considered one of the most promising solution spaces.

The LISP draft focuses on a router based solution and proposes an incremental deployment of the technology. As with map-and-encap there will be no changes to the hosts stacks and to the majority of the routers within an AS but it will be necessary to deploy some new equipment namely Ingress Tunnel Routers (ITRs) and Egress Tunnel Routers(ETRs) and possibly to develop and deploy a new Mapping System. The role of a site ITR is to find the destination locator for a local site outgoing packet by means of the Mapping System, construct and prepend the LISP header to the original IP datagram and sent the resulting packet to the ETR. The LISP header is build from the destination locator and the ITR locator. The ETR's goal is to strip down the LISP header, if the received packet has as destination address the locator of the ETR, and forward the resulting packet to the destination EID, whithin its local site. This approach also gives the possibility to implement traffic engineering and multihoming in a scalable fashion.

Through its architecture LISP seems to solve the main issues with the current routing system and offers itself as a medium term solution, until new, innovative architectures will be invented and finaly deployed. But before we can talk about a LISP DFZ zone more research is needed for the Mapping System part of the LISP architecture because as in the case of past proposals the solution itself, though elegant, introduces new scalability problems. Considerable effort is being deployed into finding what would be the best suited Mapping System both in terms of lookup latency and scalability. Among the currently proposed system are: ALT, CONS, NERD, DHT and TREE.

It is worth mentioning that at the end of March this year, 2009, the LISP WG has been formed and was chartered to submit the specifications of LISP and the ALT mapping system by March 2010.

The current paper will focus on analyzing the performances of several LISP Mapping Systems in the following chapters.

#### HIP

Host Identity Protocol [MNJH08, MN06] is another solution which aims to split the locator and the endpoint identifier roles of the IP addresses, and in fact contains as a subset the "solution space" of the SHIM6 protocol. It also incorporate a new layer into the Internet TCP/IP model between the network and the transport layer. HIP basically introduces a new 3.5-layer to avoid that sockets are bind to IP addresses forcing them to act both as the WHO and the WHERE identifiers. In HIP, upper layer sockets are bound dynamically to Host Identities (HI) instead of IP addresses.

The operation of HIP is as follows: hosts are identified with a HI that, in fact, is a public key of an asymmetric key-pair. Each host has at least one HI that can either be public or anonymous. Since public keys may have different sizes depending on the public key method HIs are represented via its 128 (SHA-1) hash, called Host Identity Tag (HIT) or via 32 bit Local Scope Identity (LSI). The HIT and LSI identify the public key that can be used for authentication purposes and are unique. HIT are mainly used for IPv6 while LSIs for IPv4. This way HIP is compatible with both versions of IP and does not require updating them.

During connection establishment HIP must be used. In this case the transport layer protocol (e.g. TCP) must be enclosed with a HIP header, which contains either the HIT or the LSI. The transport-layer end hosts are bind to this identifier, instead of the IP address. Since HITs are public keys it uses the Diffie-Hellman [Res99] key exchange to provide authentication. Additionally it can also provide confidentiality and message integrity. During the authenticated connection, mobility in HIP is quite straightforward. As HIs are used to identify the mobile node instead of IP addresses, the location of the node is not bound to the identifier. Therefore only a simple signalling protocol is needed to take care of the dynamic binding between the node's IP address and its HI. When the mobile node changes its point of attachment it simply sends a special signalling message (HIP REAddress) through the already authenticated channel. Again, since sockets are bound to HITs and not IP addresses, the connection can continue uninterrupted.

Finally a simple rendez-vous server is required to ensure reachability. This rendez-vous server is aware, through the use of some simple signalling, of the current location (IP address) of its serving HIP nodes. When another HIP-enabled node wants to establish a communication it retrieves its HIT identifier in some public address directory, such as the DNS. This directory stores both the HIT and the rendez-vous IP address. Then the node sends the initial HIP connection establishment method to the rendez-vous server, which in turn, forwards it to the actual location of the node. The remainder datagrams can be sent directly (route optimization).

The main advantages in HIP are that it does not change the architectural principles of the socket interface and that is transparent to applications. In addition since it is based in public key identifiers it relies on well-known and proven security mechanisms that provide authentication, confidentiality and message integrity. However this has also a downside, cryptographic algorithms, especially those based on asymmetric key pairs, are very costly in terms of CPU. Mobile devices have limited CPU power and HIP may impact its performance.

#### lvip

This is an independent proposal from Robin Whittle and even though it is based on the Locator/ID separation protocol its author lists in his draft [Whi07] what Ivip takes from LISP, what it leaves out and what it adds. Ivip is not treated in this paper, for further datails reading the [Whi07, Whi09] references is recommended.

#### APT

For details related to this mapping system reading [J<sup>+</sup>07] is recommended.

# 1.3 Current Implementations

### LISP+ALT Testbed

LISP+ALT is currently one of the most worked on Mapping Systems and Cisco have already implemented the protocol[FM09] in their IOS and a testbed of about 20 nodes is deployed[lis09]. The LIG (LISP Internet Groper) command has been implemented to allow users to test the network functionality.

## OpenLISP

UniversitĂŠ catholique de Louvain is currently developing an implementation of the LISP[FFML09b] protocol in the FreeBSD 7.0 kernel and have reached alpha state[ISB08].

It is the author's opinion that these implementations are not providing means of evaluating the performances of a deployed LISP routing system but only practical proof that the implemented protocols work in size constrained systems. To better analyze the performances of LISP and the LISP Mapping Systems, with the above mentioned implementations, a large scale deployment is needed, but that comes to contradiction with the obvious purpose of the analysis, to test before deployment. Thus, another approach is needed, and among the possible ones, one can intuitively guess that of building a simulator.

To the best of the author's knowledge there was no implementation of such a simulator when the work for this paper started, nor is one when the work is almost complete. In the sections which follow, an in depth, step-by-step, presentation of the implementation difficulties and results implied by the pursuit of this approach is made.

# **Chapter 2**

# **Theoretical Fundamentals**

# 2.1 Locator/Identifier Separation principle

## 2.1.1 Endpoints and Endpoint Names

In his paper [Chi99], Noel Chiappa introduces the concept of Endpoint to solve what he belives to be an overloading of the name functionality in the context of networking. There are few fundamental objects in networking, also few names and among these, good examples are, "host names" and "addresses". He has reached the conclusion that the reasons for this situation are twofold: first, this goes back as the erliest of papers in networking when the authors were not careful to distinguish between the concepts of an object and their associated names. This has caused widespread confusion between the properties of the object and those of the name. The second reason would be the lack of a rich set of fundamental objects. When dealing with new problems difficulties were encountered in finding/acknowledging the status of separate entities for previously existing, but "masked" objects.

In the days of the ARPANET the "address" had a straightforward meaning and was build by concatenating the number of the host with a port number. But as the scale of the internet has grown, the "tight" association between the functions of the term "address" and this sole "instantiation" of the name has stemed confusion. Chiappa and Saltzer [Sal93] explain this by the small number of well defined concepts at hand.

To set asside the confusion it was proposed that the term "address" should be redefined and used with one of the current implied uses and be limited to this particular one. Also, the fundamental object, the "endpoint" is defined. In fact, it is acknowledged as previously present in the network but unnamed.

For a better understanding of the technical aspects, the author, also definies bindings and namespaces. The binding being the association between a name and an object, but they may also map from one "kind" of name to another. Furthermore, instances of the same object may have more than one name and these names may be from the same class of names, or otherwise "namespace". Depending on the namespaces we may have many-to-one bindings or alternatively many one-to-one bindings.

The relation between the structure of the names in a namespace and the function is also observed. This may be explained by the need for ease of use and a good example would be the structure implied by the IP addresses in order to ease routing. It is also obvious that names may have multiple ways of representation (eg. decimal printed notations and the bit representation for IPs)

The namespaces togheter with the possibility to represent names in multiple ways imply the existance of contexts which may help make the distinction between attachment of names to objects and mappings from one namespace to another.

All the above theoretical introduction can be used now to analyze the TCP/IP Architecture which did not make a clear distinction between the objects and the names of those objects. In fact it can be observed that the namespaces are as old as the NCP prococol architecture, namely the addresses and the host-names.

IP addresses are in fact the only "names" used throughout the TCP/IP architecture but they have multiple uses:

- Used by the routers when forwarding the user data packets

- Used to name a place in the network, the destination of a packet. Otherwise known as the "network attachment point" or "interface"

- Used in transport layer identifiers for both of the end-to-end communicating hosts.

The overloading of this single name and "field" with all these functionalities is not for the best and a soulution would be to split these three functions up, and have them performed by separete fields.

The other TCP/IP architecture namespace is that of host-names. They are human readable strings and contained in a hierarchical structure and can be looked up in the distributed and replicated database we all know as the DNS (Domain Name System). But their goal is, in fact, to map between the human readable characters and one or several IP addresses which will mediatate the TCP "conversation" between the hosts, once determined.

As expected, the double function of the IP addresses, that of identifying the interfaces and the hosts has downsides and an important one is the limitations of host mobility. This is because a TCP connection, as already mentioned, is always identified by the pair IP address and TCP port. It only follows that a change of the IP address, requested by the change of the position in the internetwork, will brake the TCP connection.