# A NETWORK ARCHITECTURE FOR SUPPORTING PARALLEL COMPUTING OVER ATM

A DOCTORAL THESIS

Author:Joan Vila i SallentAdvisor:Josep Solé i Pareta

UNIVERSITAT POLITÈCNICA DE CATALUNYA Departament d'Arquitectura de Computadors

Barcelona, September 1997

## Contents

| Li | st of F | igures        |                                                        | vii  |

|----|---------|---------------|--------------------------------------------------------|------|

| Li | st of 1 | <b>Tables</b> |                                                        | xi   |

| Pr | eface   |               |                                                        | xiii |

| Ac | cknow   | ledgme        | ents                                                   | xvii |

| 1  | Intro   | oductior      | ı                                                      | 1    |

|    | 1.1     | Motiva        | ation and contributions                                | . 1  |

|    | 1.2     | The sc        | enario                                                 | . 2  |

|    |         | 1.2.1         | Parallel computing and Networks of Workstations (NoWs) | . 2  |

|    |         | 1.2.2         | A public platform based on the NoW concept             | . 5  |

|    | 1.3     | Conce         | pts of ATM technology                                  | . 7  |

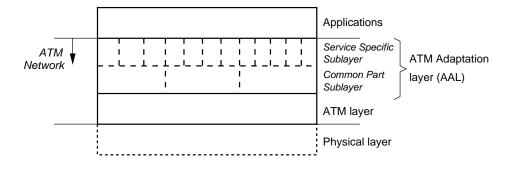

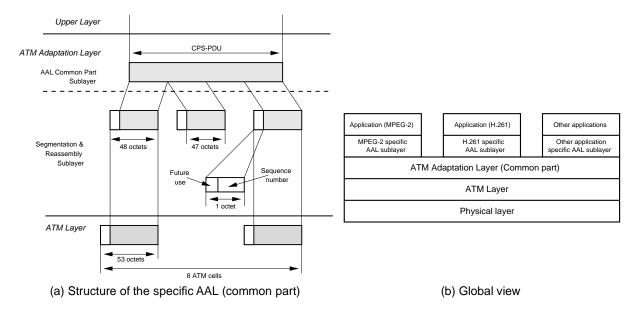

|    |         | 1.3.1         | Architecture of ATM networks                           | . 7  |

|    |         | 1.3.2         | Services provided in the ATM layer                     | . 8  |

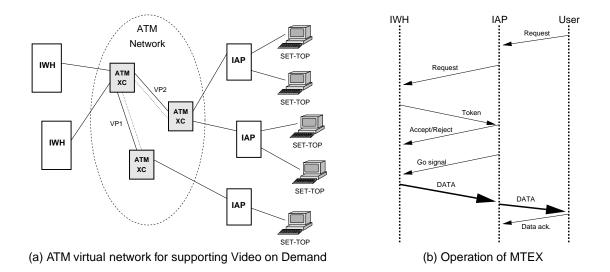

|    |         | 1.3.3         | Services provided in the ATM Adaptation Layer          | . 11 |

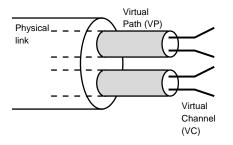

|    |         | 1.3.4         | Possibility of virtual subnetworks                     | . 13 |

|    | 1.4     | Measu         | ring communications performance                        | . 15 |

|    |         | 1.4.1         | Performance parameters                                 | . 15 |

|    |         | 1.4.2         | Performance of parallel computing applications         | . 16 |

| 2  | Pote    | ential pe     | erformance of ATM in Networks of Workstations          | 17   |

|    | 2.1     | Perform       | mance under ideal conditions                           | . 17 |

|    | 2.2     | Bottler       | neck analysis in ATM-based environments                | . 20 |

|    |         | 2.2.1         | Experiment 1: Impact of network load and network size  | . 20 |

|    |         | 2.2.2         | Experiment 2: Estimation of cell loss                  | . 22 |

|    |         | 2.2.3         | Experiment 3: Impact of host delay and network load    | . 24 |

|    | 2.3     | Discus        | ssion                                                  | . 24 |

| Stra | tegies fo                                                                                                                                                  | or introducing ATM in parallel environments                                                                                                                                                                                                                                                                                                                                                       | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.1  | Traditio                                                                                                                                                   | onal protocols over ATM                                                                                                                                                                                                                                                                                                                                                                           | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | 3.1.1                                                                                                                                                      | Interfaces between existing protocols and ATM                                                                                                                                                                                                                                                                                                                                                     | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

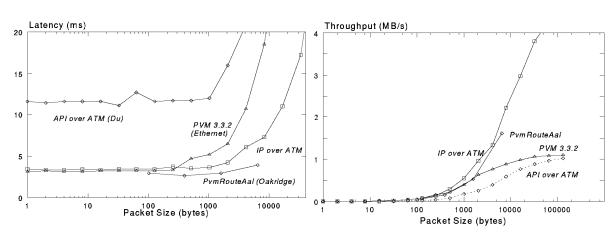

|      | 3.1.2                                                                                                                                                      | Performance studies                                                                                                                                                                                                                                                                                                                                                                               | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

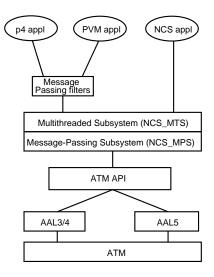

| 3.2  | Introdu                                                                                                                                                    | cing an ATM-specific API                                                                                                                                                                                                                                                                                                                                                                          | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

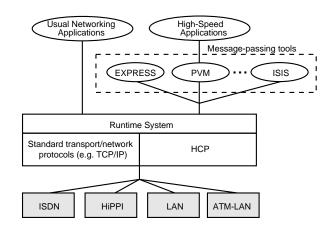

|      | 3.2.1                                                                                                                                                      | The ATM API                                                                                                                                                                                                                                                                                                                                                                                       | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | 3.2.2                                                                                                                                                      | Performance without an adapted message-passing library                                                                                                                                                                                                                                                                                                                                            | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | 3.2.3                                                                                                                                                      | Performance with adapted message-passing libraries                                                                                                                                                                                                                                                                                                                                                | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | 3.2.4                                                                                                                                                      | Discussion                                                                                                                                                                                                                                                                                                                                                                                        | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.3  | Specifi                                                                                                                                                    | c mechanisms for parallel computing                                                                                                                                                                                                                                                                                                                                                               | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | 3.3.1                                                                                                                                                      | API-level enhancement mechanisms                                                                                                                                                                                                                                                                                                                                                                  | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | 3.3.2                                                                                                                                                      | Transport-level mechanisms                                                                                                                                                                                                                                                                                                                                                                        | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

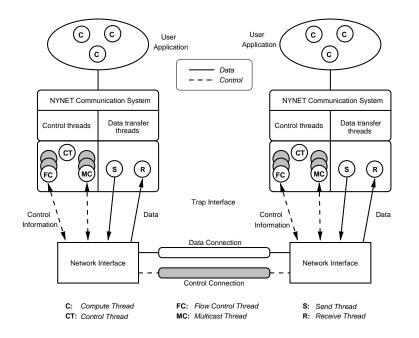

|      | 3.3.3                                                                                                                                                      | Application-level mechanisms                                                                                                                                                                                                                                                                                                                                                                      | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | 3.3.4                                                                                                                                                      | Discussion                                                                                                                                                                                                                                                                                                                                                                                        | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      |                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                   | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | -                                                                                                                                                          | -                                                                                                                                                                                                                                                                                                                                                                                                 | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4.2  | _                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                   | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                   | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                   | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |                                                                                                                                                            | · · · ·                                                                                                                                                                                                                                                                                                                                                                                           | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |                                                                                                                                                            | -                                                                                                                                                                                                                                                                                                                                                                                                 | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4.3  | Summa                                                                                                                                                      | ary                                                                                                                                                                                                                                                                                                                                                                                               | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Cou  | pling SS                                                                                                                                                   | SCOP with ATM-based parallel computing                                                                                                                                                                                                                                                                                                                                                            | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.1  | Descrip                                                                                                                                                    | ption of SSCOP basic functionality                                                                                                                                                                                                                                                                                                                                                                | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | 5.1.1                                                                                                                                                      | Interest of SSCOP in ATM networks                                                                                                                                                                                                                                                                                                                                                                 | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

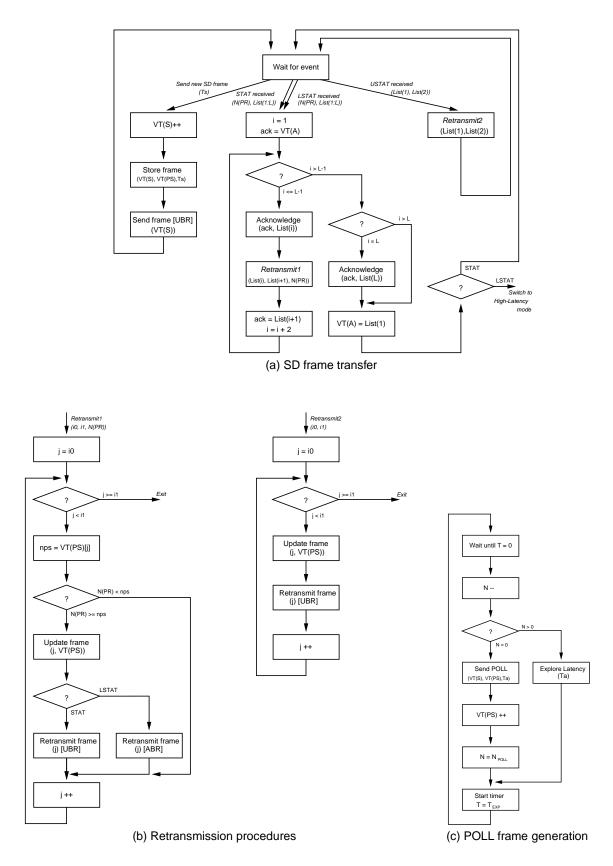

|      | 5.1.2                                                                                                                                                      | Operation of the loss recovery mechanism                                                                                                                                                                                                                                                                                                                                                          | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.2  | Modifie                                                                                                                                                    | cations to SSCOP                                                                                                                                                                                                                                                                                                                                                                                  | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | 5.2.1                                                                                                                                                      | The "frame corruption by cell loss" problem                                                                                                                                                                                                                                                                                                                                                       | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

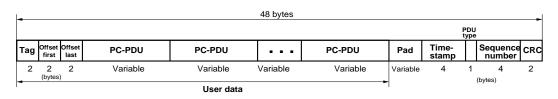

|      | 5.2.2                                                                                                                                                      | Cell-based PDU mapping                                                                                                                                                                                                                                                                                                                                                                            | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | 5.2.3                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                   | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.3  | Experii                                                                                                                                                    | -                                                                                                                                                                                                                                                                                                                                                                                                 | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | 5.3.1                                                                                                                                                      | Measurement scenario                                                                                                                                                                                                                                                                                                                                                                              | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

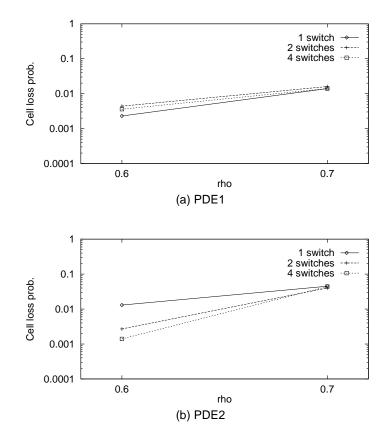

|      | 5.3.2                                                                                                                                                      | Behavior of PDE1                                                                                                                                                                                                                                                                                                                                                                                  | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | 5.3.3                                                                                                                                                      | Behavior of PDE2 and SOLVER                                                                                                                                                                                                                                                                                                                                                                       | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | 5.3.4                                                                                                                                                      | Confidence of results                                                                                                                                                                                                                                                                                                                                                                             | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | <ul> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li><b>The</b></li> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li><b>Cou</b></li> <li>5.1</li> <li>5.2</li> </ul> | 3.1 Tradition<br>3.1 Tradition<br>3.1.1<br>3.1.2<br>3.2 Introduc<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.3 Specified<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>The network<br>4.1 Integrat<br>4.2 Specified<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.3 Summa<br>Coupling SS<br>5.1 Descript<br>5.1.1<br>5.1.2<br>5.2 Modified<br>5.2.1<br>5.2.2<br>5.2.3<br>5.3 Experint<br>5.3.1<br>5.3.2<br>5.3.3 | 3.1.1       Interfaces between existing protocols and ATM         3.1.2       Performance studies         3.2       Introducing an ATM-specific API         3.2.1       The ATM API         3.2.2       Performance without an adapted message-passing libraries         3.2.3       Performance with adapted message-passing libraries         3.2.4       Discussion         3.3       Specific mechanisms for parallel computing         3.3.1       API-level enhancement mechanisms         3.3.2       Transport-level mechanisms         3.3.3       Application-level mechanisms         3.3.4       Discussion         The network architecture model         4.1       Integration of specific mechanisms over ATM         4.2       Specific architecture for parallel computing         4.2.1       Overlay network for signaling in parallel computing         4.2.2       Protocol architecture         4.2.3       Requirements for the Application Level         4.2.4       Architecture of the Convergence Level         4.3       Summary         5.1       Interest of SSCOP basic functionality         5.1.1       Interest of SSCOP         5.2.2       Cell-based PDU mapping         5.2.3       Encapsulation schemes     < |

|     | 5.4         | Discussion                                                     | 76 |

|-----|-------------|----------------------------------------------------------------|----|

| 6   | Expl        | oitation of ATM services                                       | 79 |

|     | 6.1         | Enhancing the Parallel Computing AAL                           | 79 |

|     |             | 6.1.1 Introducing ATM service categories                       | 79 |

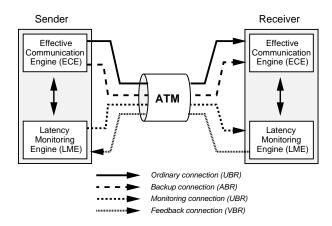

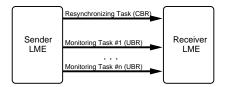

|     |             | 6.1.2 The Latency Monitoring Engine (LME)                      | 80 |

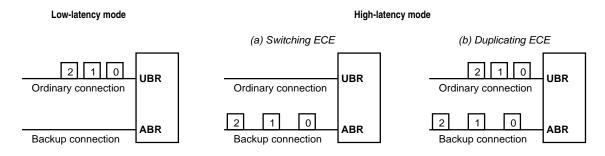

|     |             | 6.1.3 The Effective Communication Engine (ECE)                 | 82 |

|     | 6.2         | Performance measurements                                       | 89 |

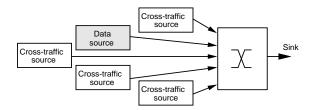

|     |             | 6.2.1 Experiment configuration                                 | 91 |

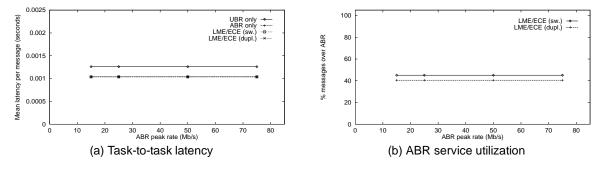

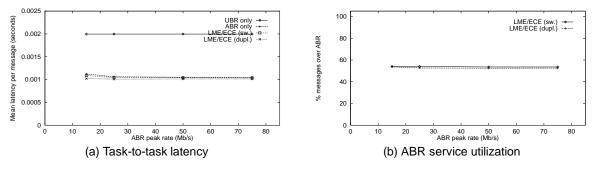

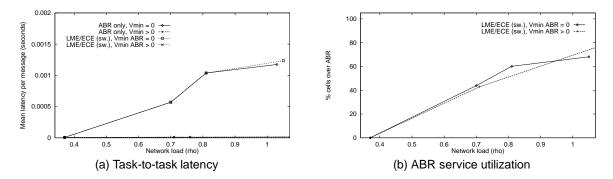

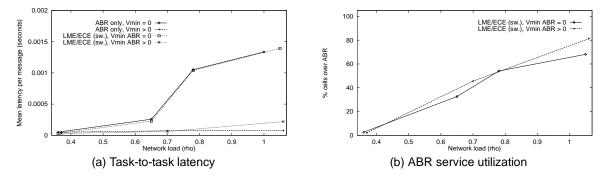

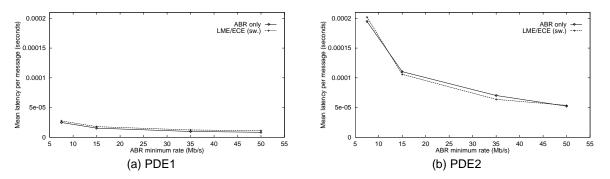

|     |             | 6.2.2 Task-to-task latency                                     | 93 |

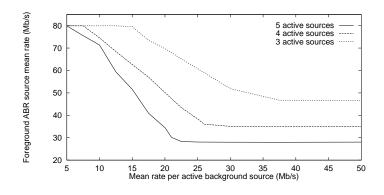

|     |             | 6.2.3 ABR service utilization                                  | 96 |

|     |             | 6.2.4 Bandwidth consumption                                    | 97 |

|     |             | 6.2.5 Influence of the ABR peak rate                           | 98 |

|     |             | 6.2.6 ABR with a minimum guaranteed cell rate                  | 99 |

|     |             | 6.2.7 Confidence of results                                    | 00 |

|     | 6.3         | Discussion                                                     | 01 |

| 7   | Cond        | clusions and future work 1                                     | 03 |

|     | 7.1         | Summary of contributions                                       | 03 |

|     |             | 7.1.1 Potential performance of ATM-based platforms             | 03 |

|     |             | 7.1.2 The network architecture                                 | 04 |

|     |             | 7.1.3 The mechanisms for implementing the network architecture | 05 |

|     | 7.2         | Future work                                                    | 06 |

| Α   | Bend        | chmarks 1                                                      | 09 |

|     | A.1         | Description                                                    | 09 |

|     | A.2         | Characteristics of communications                              | 10 |

| в   | Emu         | lation of an ATM network 1                                     | 13 |

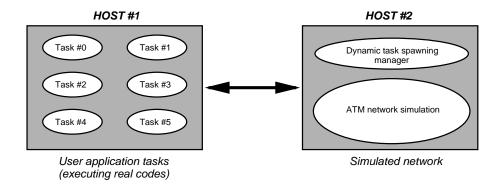

|     | <b>B</b> .1 | Objectives and description                                     | 13 |

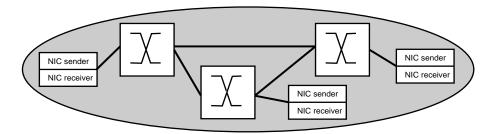

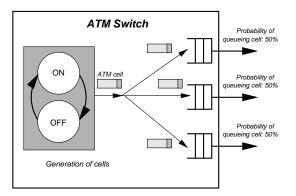

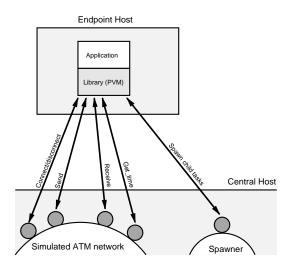

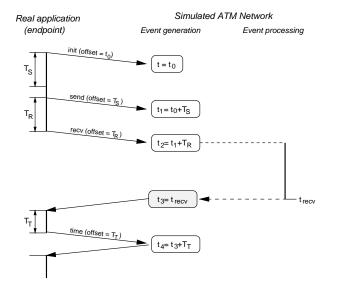

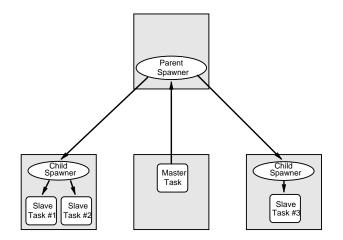

|     |             | B.1.1 ATM network simulation                                   | 14 |

|     |             | B.1.2 Interface with real applications                         | 15 |

|     | B.2         | Validation and verification                                    | 17 |

|     |             | B.2.1 Verification of message sequence & data integrity        | 17 |

|     |             | B.2.2 Validation of measurements                               | 18 |

| Bil | oliogr      | aphy 1                                                         | 21 |

CONTENTS

# **List of Figures**

### Chapter 1

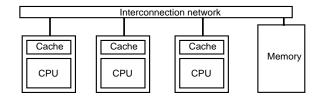

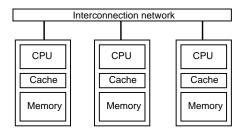

| 1.1 | Architecture of a shared-memory system.                            | 3  |

|-----|--------------------------------------------------------------------|----|

| 1.2 | Distributed memory architecture.                                   | 4  |

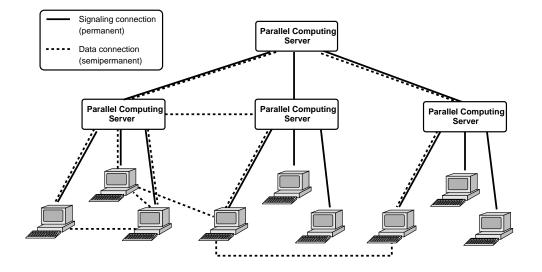

| 1.3 | Network of Workstations (NoW).                                     | 5  |

| 1.4 | Architecture of ATM networks.                                      | 7  |

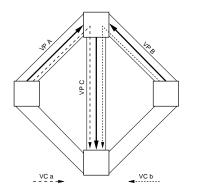

| 1.5 | The VP concept: Virtual Channels multiplexed within Virtual Paths. | 14 |

| 1.6 | Example of virtual subnetwork by concatenating VPs.                | 14 |

## Chapter 2

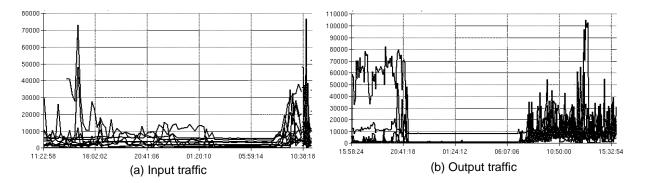

| 2.1 | 24-hour Ethernet traffic in the department, measured in the internal subnetwork attachment. | 18 |

|-----|---------------------------------------------------------------------------------------------|----|

| 2.2 | Performance for different network sizes                                                     | 21 |

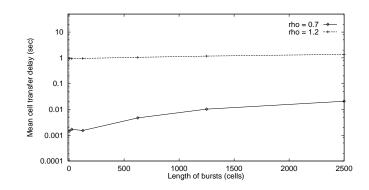

| 2.3 | Impact of network load and burst size on communications latency.                            | 22 |

| 2.4 | Cell loss for different configurations.                                                     | 23 |

| 2.5 | Performance for different host delays.                                                      | 25 |

### Chapter 3

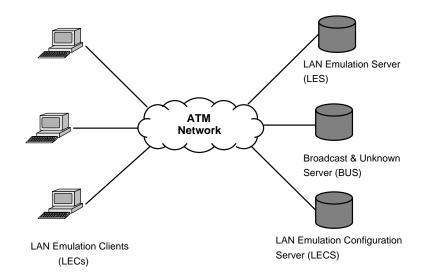

| 3.1 | LAN Emulation architecture.                                                    | 28 |

|-----|--------------------------------------------------------------------------------|----|

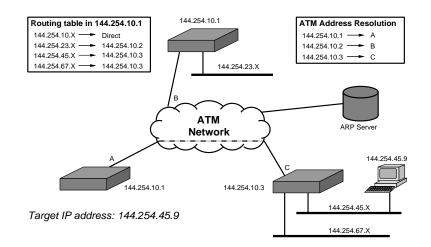

| 3.2 | IP routing across an ATM network.                                              | 29 |

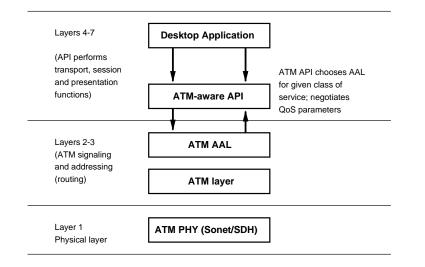

| 3.3 | Native ATM API-based architecture.                                             | 32 |

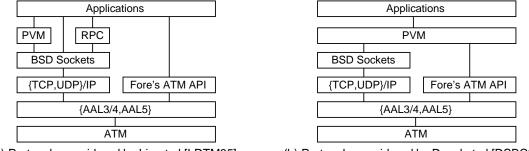

| 3.4 | Protocol stacks for ATM-API-based architectures.                               | 33 |

| 3.5 | Performance of several software structures obtained by Dowd et al [DSBC95]     | 34 |

| 3.6 | Dedicated protocol environment for parallel computing                          | 37 |

| 3.7 | Architecture of a multithreading environment for supporting parallel computing | 38 |

| 3.8 | Multithreading support for distributed parallel computing                      | 39 |

### Chapter 4

| 4.1 | Specific architecture | for supporting mul | timedia applications | s suggested in [GVH96]. | 43 |

|-----|-----------------------|--------------------|----------------------|-------------------------|----|

|-----|-----------------------|--------------------|----------------------|-------------------------|----|

| 4.2 | Specific architecture for supporting the Video on Demand Service as suggested in [CF96]. | 43 |

|-----|------------------------------------------------------------------------------------------|----|

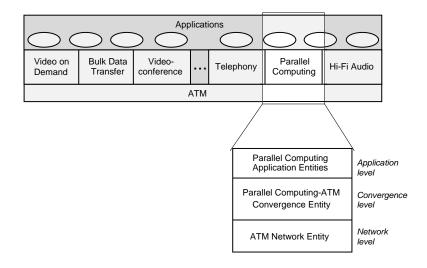

| 4.3 | Integration of services over ATM.                                                        | 44 |

| 4.4 | A virtual ring overlay network                                                           | 45 |

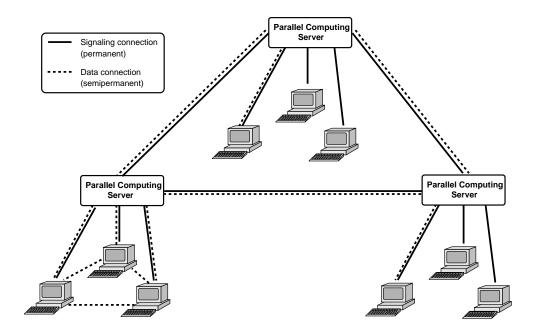

| 4.5 | A virtual tree overlay network.                                                          | 46 |

## Chapter 5

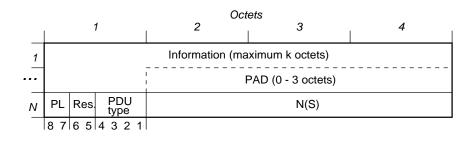

| 5.1  | SSCOP SD frame format.                                                                                                                                                | 55 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.2  | SSCOP POLL frame format                                                                                                                                               | 56 |

| 5.3  | SSCOP STAT frame format.                                                                                                                                              | 56 |

| 5.4  | SSCOP USTAT frame format.                                                                                                                                             | 56 |

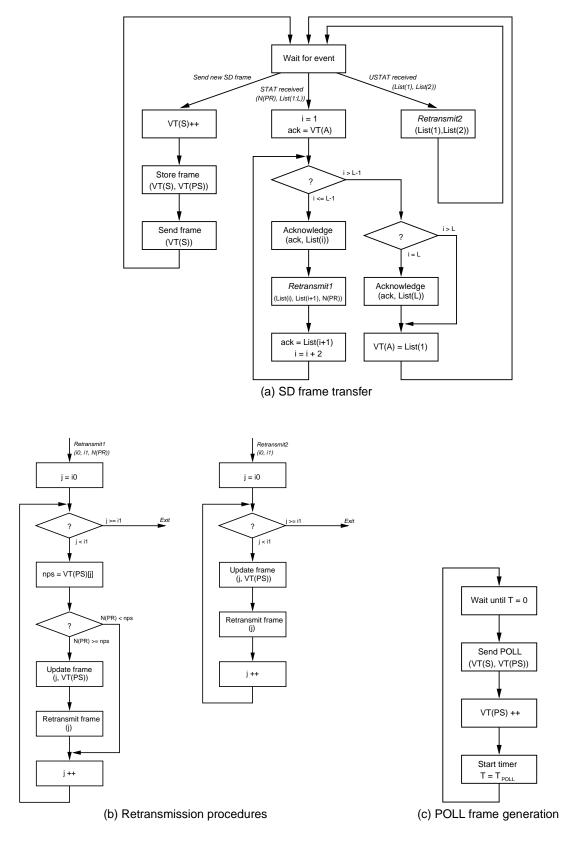

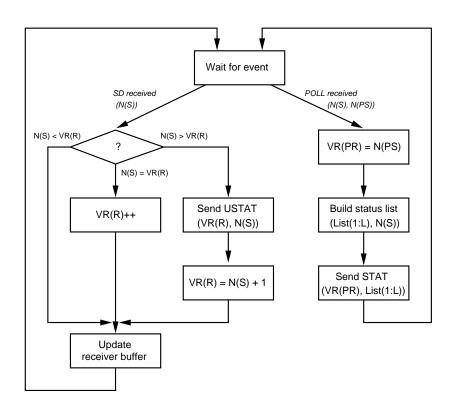

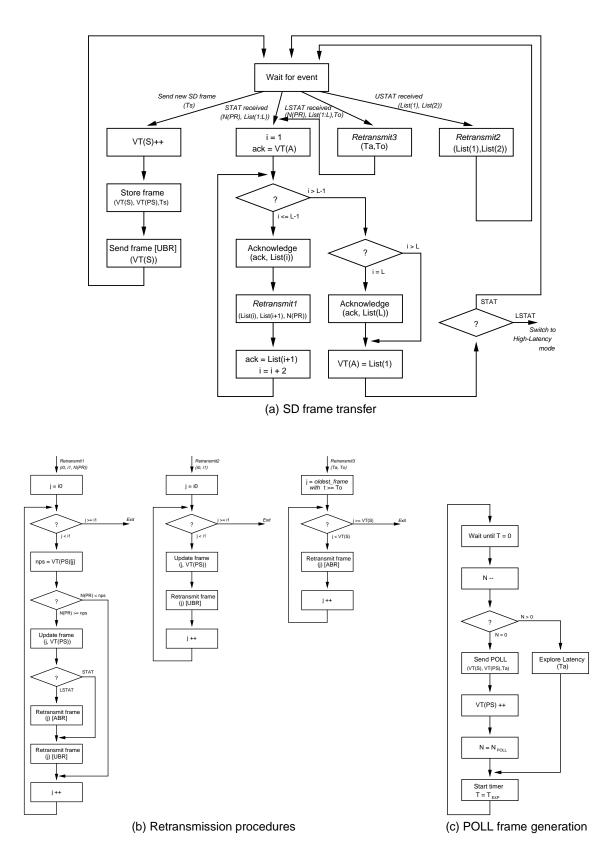

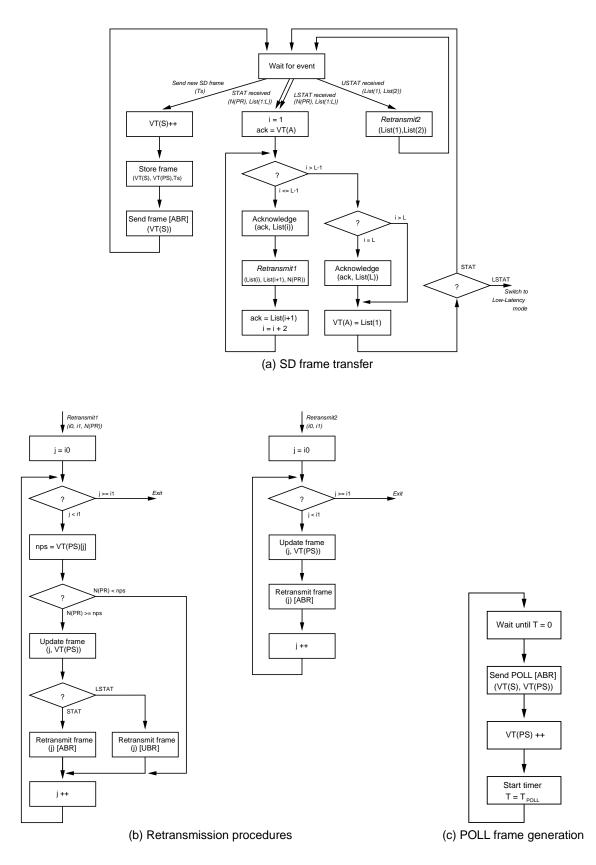

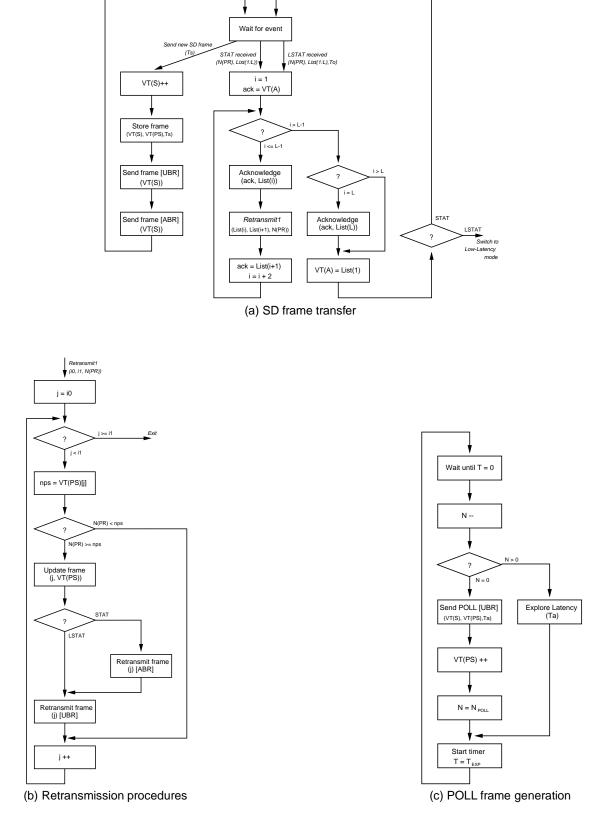

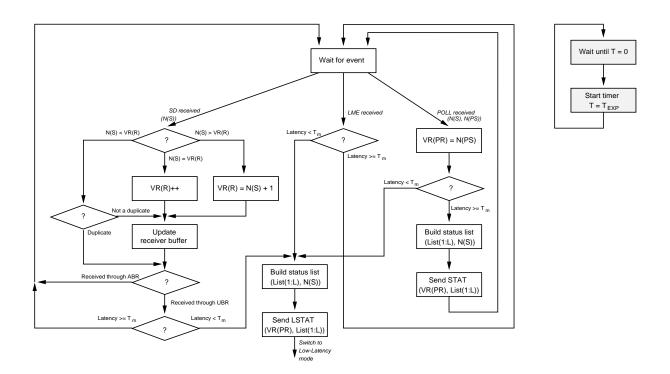

| 5.5  | SSCOP sender behavior flowchart                                                                                                                                       | 58 |

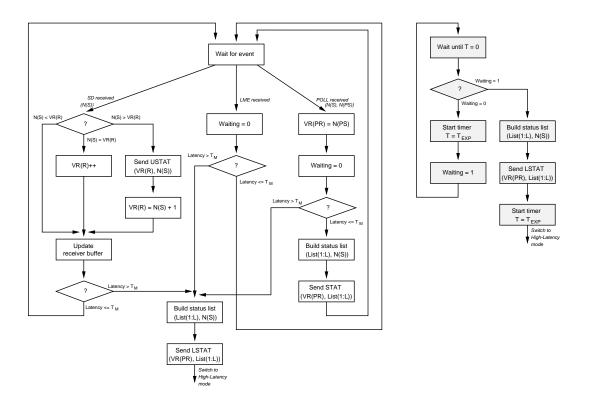

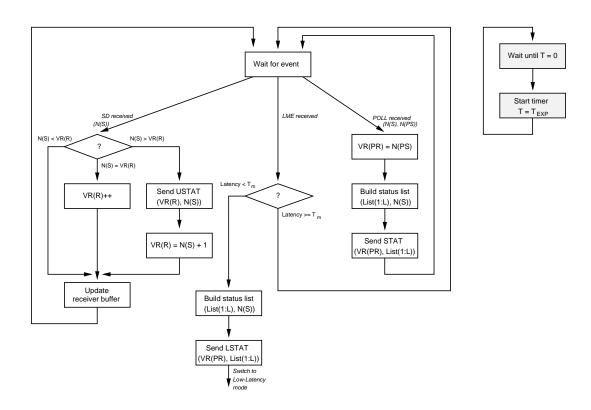

| 5.6  | SSCOP receiver behavior flowchart.                                                                                                                                    | 59 |

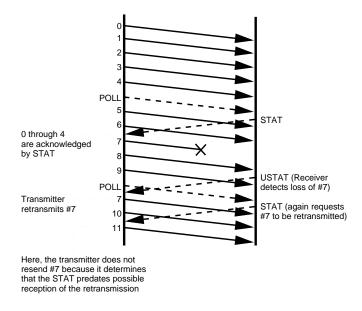

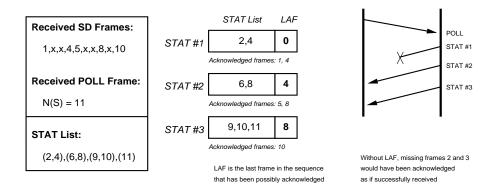

| 5.7  | Example of SSCOP operation.                                                                                                                                           | 60 |

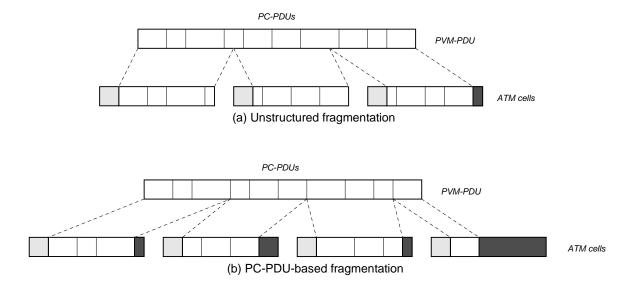

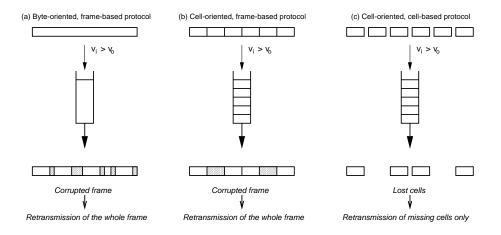

| 5.8  | Fragmentation strategies                                                                                                                                              | 62 |

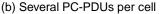

| 5.9  | Encapsulation schemes for SD frames (sizes in bytes)                                                                                                                  | 63 |

| 5.10 | Structure of a PVM message.                                                                                                                                           | 64 |

| 5.11 | Example of issuing a STAT sequence.                                                                                                                                   | 65 |

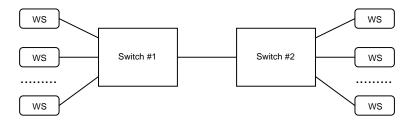

| 5.12 | Simulated environment.                                                                                                                                                | 65 |

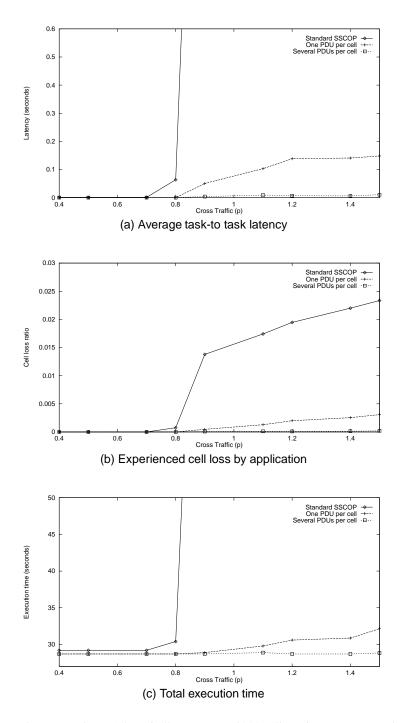

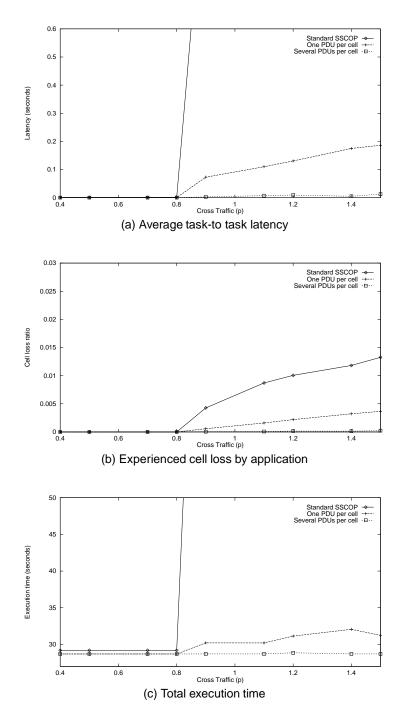

| 5.13 | Performance of PDE1 for a buffer capacity of 200 cells and a POLL interval of 0.5 seconds.                                                                            | 69 |

| 5.14 | Why cell-based fragmentation leads to stability.                                                                                                                      | 70 |

| 5.15 | Performance of PDE1 for a buffer capacity of $1000$ cells and a POLL interval of $0.5$ seconds.                                                                       | 71 |

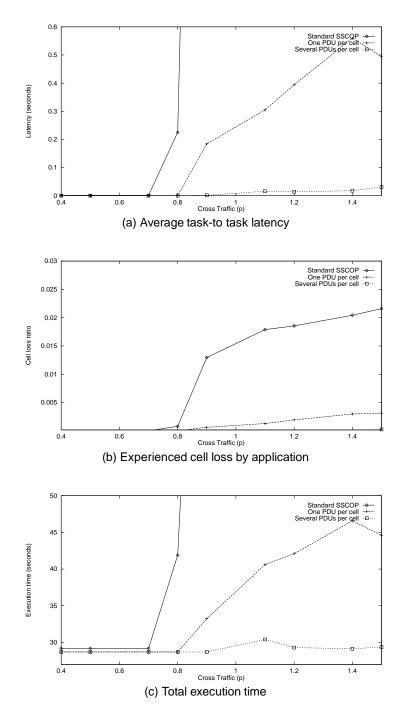

| 5.16 | Performance of PDE1 for a buffer capacity of 200 cells and a POLL interval of 1.5 second.                                                                             | 73 |

| 5.17 | Latency and cell loss of PDE1, PDE2, and SOLVER for a buffer capacity of 200 cells and a POLL interval of 0.5 seconds. Encapsulation scheme: several PC-PDUs per cell | 74 |

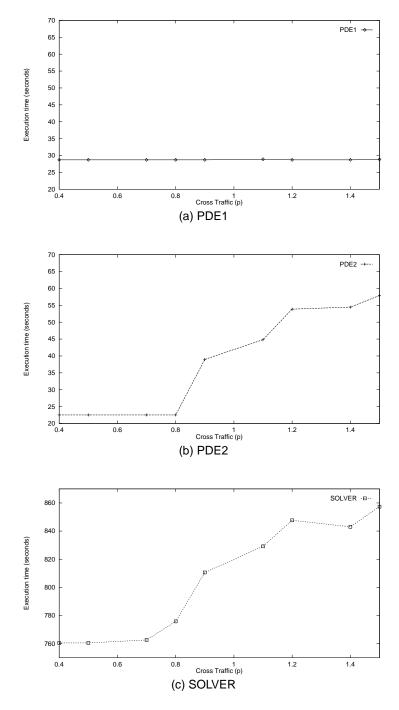

| 5.18 | Execution time of PDE1, PDE2, and SOLVER for a buffer capacity of 200 cells and a POLL interval of 0.5 seconds. Encapsulation scheme: several PC-PDUs per cell        | 75 |

## Chapter 6